VNC1L –Є –≤—Б–µ, –≤—Б–µ, –≤—Б–µ - –Ю—Б–Њ–±–µ–љ–љ–Њ—Б—В–Є SPI –Є–љ—В–µ—А—Д–µ–є—Б–∞

–Ю—Б–Њ–±–µ–љ–љ–Њ—Б—В–Є SPI –Є–љ—В–µ—А—Д–µ–є—Б–∞

SPI –Є–љ—В–µ—А—Д–µ–є—Б, —А–µ–∞–ї–Є–Ј–Њ–≤–∞–љ–љ–∞–є –≤ AVR –љ–µ –Є–Љ–µ–µ—В –љ–Є–Ї–∞–Ї–Њ–≥–Њ –Њ—В–љ–Њ—И–µ–љ–Є—П –Ї SPI –Є–љ—В–µ—А—Д–µ–є—Б—Г вАЬ–Т–Є–љ–љ–ЄвАЭ. –Ш—Б—Е–Њ–і—П –Є–Ј —Н—В–Њ–≥–Њ 4 –љ–Њ–≥–Є AVR, —А–µ–∞–ї–Є–Ј—Г—О—Й–Є–µ –≤–Ј–∞–Є–Љ–Њ–і–µ–є—Б—В–≤–Є–µ –Љ–Њ–≥—Г—В –±—Л—В—М –ї—О–±—Л–Љ–Є. –Ф–Є–∞–≥—А–∞–Љ–Љ—Л –≤–Ј–∞–Є–Љ–Њ–і–µ–є—Б—В–≤–Є—П —А–µ–∞–ї–Є–Ј–Њ–≤–∞–љ—Л –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ. вАЬ–Т–Є–љ–љ–ЄвАЭ, –Ї–∞–Ї SPI —Г—Б—В—А–Њ–є—Б—В–≤–Њ –Љ–Њ–ґ–µ—В –±—Л—В—М —В–Њ–ї—М–Ї–Њ SLAVE. –†–µ–ґ–Є–Љ SPI –≤—Л–±–Є—А–∞–µ—В—Б—П –љ–Њ–≥–∞–Љ–Є 46 –Є 47 вАЬ–Т–Є–љ–љ–ЄвАЭ –Є –љ–Є–Ї–∞–Ї –љ–µ —Б–≤—П–Ј–∞–љ —Б –њ—А–Њ—И–Є–≤–Ї–Њ–є. –Т—Б–µ–≥–Њ —Б—Г—Й–µ—Б—В–≤—Г–µ—В —В—А–Є —А–µ–ґ–Є–Љ–∞ –≤–Ј–∞–Є–Љ–Њ–і–µ–є—Б—В–≤–Є—П –љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ—П:

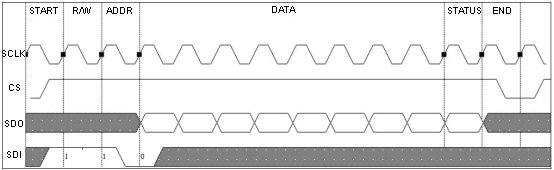

–І—В–µ–љ–Є–µ –±–∞–є—В–∞ –і–∞–љ–љ—Л—Е:

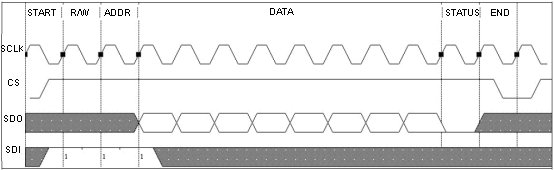

–І—В–µ–љ–Є–µ –±–∞–є—В–∞ —Б—В–∞—В—Г—Б–∞:

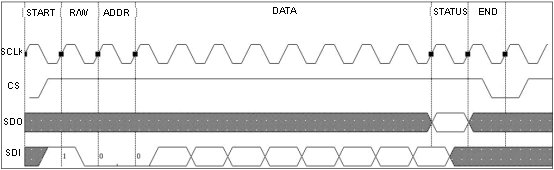

–Ч–∞–њ–Є—Б—М –±–∞–є—В–∞ –і–∞–љ–љ—Л—Е:

–Ъ–∞–Ї –≤–Є–і–љ–Њ –Є–Ј –і–Є–∞–≥—А–∞–Љ–Љ —Б–Є–≥–љ–∞–ї CS –∞–Ї—В–Є–≤–µ–љ –њ–Њ –≤—Л—Б–Њ–Ї–Њ–Љ—Г —Г—А–Њ–≤–љ—О, —З—В–Њ –љ–µ —П–≤–ї—П–µ—В—Б—П –Њ–±—Й–µ–њ—А–Є–љ—П—В—Л–Љ. –Ч–∞–њ–Є—Б—М –±–Є—В–∞ –њ—А–Њ–Є—Б—Е–Њ–і–Є—В –њ–Њ –њ–µ—А–µ–і–љ–µ–Љ—Г —Д—А–Њ–љ—В—Г SCLK. –°—Г—Й–µ—Б—В–≤—Г–µ—В —В—А–Є —Д–∞–Ј—Л –і–Є–∞–≥—А–∞–Љ–Љ—Л:

- вАҐ –Я–Њ–і–≥–Њ—В–Њ–≤–Є—В–µ–ї—М–љ–∞—П, –≥–і–µ –Њ–њ—А–µ–і–µ–ї—П–µ—В—Б—П –љ–∞–њ—А–∞–≤–ї–µ–љ–Є–µ –њ–µ—А–µ–і–∞—З–Є (–І—В–µ–љ–Є–µ/–Ч–∞–њ–Є—Б—М) –Є –∞–і—А–µ—Б—Б. (3 —Ж–Є–Ї–ї–∞)

- вАҐ –§–∞–Ј–∞ –њ–µ—А–µ–і–∞—З–Є –±–є—В–∞ –і–∞–љ–љ—Л—Е. (8 —Ж–Є–Ї–ї–Њ–≤)

- вАҐ –Ч–∞–≤–µ—А—И–∞—О—Й–∞—П, –≥–і–µ –њ—А–Њ–Є—Б—Е–Њ–і–Є—В —З—В–µ–љ–Є–µ —Б—В–∞—В—Г—Б–љ–Њ–≥–Њ –±–Є—В–∞, –Є –Ј–∞–≤–µ—А—И–µ–љ–Є–µ CS. (2 —Ж–Є–Ї–ї–∞)

–Т—Б–µ–≥–Њ –≤–Ј–∞–Є–Љ–Њ–і–µ–є—Б—В–≤–Є–µ –њ—А–Њ–Є—Б—Е–Њ–і–Є—В –Ј–∞ 13 —Ж–Є–Ї–ї–Њ–≤ SCLK.

–°—В–∞—В—Г—Б–љ—Л–є –±–Є—В –Њ–њ—А–µ–і–µ–ї—П–µ—В –њ—А–∞–≤–Є–ї—М–љ–Њ—Б—В—М –њ—А–Њ—Е–Њ–ґ–і–µ–љ–Є—П –≤—Б–µ–є –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ—Б—В–Є –љ–∞ –љ–Є–Ј–Ї–Њ–Љ —Г—А–Њ–≤–љ–µ. –Х–≥–Њ —Б—Г—В—М –њ—А–Њ—Б—В–∞, –µ—Б–ї–Є —Б—В–∞—В—Г—Б–љ—Л–є –±–Є—В —А–∞–≤–µ–љ –љ—Г–ї—О, –≤—Б–µ –Ю–Ъ. –Т –њ—А–Њ—В–Є–≤–љ–Њ–Љ —Б–ї—Г—З–∞–µ –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ –њ–Њ–≤—В–Њ—А–Є—В—М –і–Є–∞–≥—А–∞–Љ–Љ—Г. –≠—В–Њ —Б–њ—А–∞–≤–µ–і–ї–Є–≤–Њ –і–ї—П –≤—Б–µ—Е —В—А—С—Е —А–µ–ґ–Є–Љ–Њ–≤. –Х—Б–ї–Є —З–Є—В–∞–µ—В—Б—П –±–∞–є—В —Б—В–∞—В—Г—Б–∞, –±–Є—В —Б—В–∞—В—Г—Б–∞ –њ—А–Є —Н—В–Њ–Љ –≤—Б–µ–≥–і–∞ –љ–Њ–ї—М.

| –С–Є—В –љ–∞–њ—А–∞–≤–ї–µ–љ–Є—П (R/W) | –С–Є—В –∞–і—А–µ—Б–∞ (ADDR) | –Ю–њ–µ—А–∞—Ж–Є—П |

| 1 | 0 | –І—В–µ–љ–Є–µ –±–∞–є—В–∞ –і–∞–љ–љ—Л—Е –≤ –±—Г—Д–µ—А –њ—А–Є–µ–Љ–љ–Є–Ї–∞ |

| 1 | 1 | –І—В–µ–љ–Є–µ –±–∞–є—В–∞ —Б—В–∞—В—Г—Б–∞ |

| 0 | 0 | –Ч–∞–њ–Є—Б—М –±–∞–є—В–∞ –і–∞–љ–љ—Л—Е –≤ –±—Г—Д–µ—А –њ–µ—А–µ–і–∞—В—З–Є–Ї–∞ |

–С–∞–є—В —Б—В–∞—В—Г—Б–∞ –Њ–њ—А–µ–і–µ–ї—П–µ—В –≤–Ј–∞–Є–Љ–Њ–і–µ–є—Б—В–≤–Є–µ –љ–∞ –±–Њ–ї–µ–µ –≤—Л—Б–Њ–Ї–Њ–Љ —Г—А–Њ–≤–љ–µ, —Н—В–Њ —Г—А–Њ–≤–µ–љ—М –њ–µ—А–µ–і–∞—З–Є –Ї–Њ–Љ–∞–љ–і –Є –њ–Њ–ї—Г—З–µ–љ–Є–µ –Њ—В–≤–µ—В–∞. –І—В–Њ–±—Л —Б–Є–љ—Е—А–Њ–љ–Є–Ј–Є—А–Њ–≤–∞—В—М —Н—В–Є –≤–Ј–∞–Є–Љ–Њ–і–µ–є—Б—В–≤–Є—П –≤ вАЬ–Т–Є–љ–љ–ЄвАЭ –µ—В—М –±—Г—Д–µ—А –њ—А–Є–µ–Љ–љ–Є–Ї–∞ –Є –±—Г—Д–µ—А –њ–µ—А–µ–і–∞—В—З–Є–Ї–∞. –Ш—Е —Б–Њ—Б–Њ—В—П–љ–Є–µ –Њ–њ—А–µ–і–µ–ї—П–µ—В—Б—П –Ј–љ–∞—З–µ–љ–Є–µ–Љ –±–Є—В–Њ–≤ –±–∞–є—В–∞ —Б—В–∞—В—Г—Б–∞.

| –С–Є—В—Л | –Ч–љ–∞—З–µ–љ–Є–µ | –°–Њ—Б—В–Њ—П–љ–Є–µ |

| Bit0 | 0 | –С—Г—Д–µ—А –њ—А–Є–µ–Љ–љ–Є–Ї–∞ –њ—Г—Б—В |

| 1 | –С—Г—Д–µ—А –њ—А–Є–µ–Љ–љ–Є–Ї–∞ –Ј–∞–њ–Њ–ї–љ–µ–љ | |

| Bit1 | 0 | –С—Г—Д–µ—А –њ–µ—А–µ–і–∞—В—З–Є–Ї–∞ –Ј–∞–њ–Њ–ї–љ–µ–љ |

| 1 | –С—Г—Д–µ—А –њ–µ—А–µ–і–∞—В—З–Є–Ї–∞ –њ—Г—Б—В | |

| Bit4 | ||

| Bit5 |

–Ю–±–љ–Њ–≤–ї–µ–љ–Њ (17.06.2012 09:04)